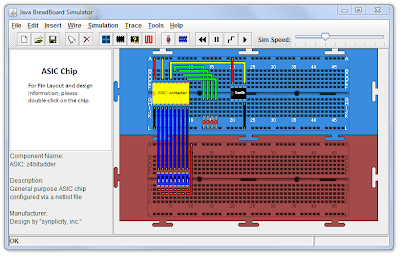

Our department created through several student projects a digital circuit simulator in Java.

It allows users to add a variety of different components, wire them up and then simulate them. Great for electronics hobbyists or students.

What I did was extend this so Field Programmable Gate Arrays (FPGA's) could be simulated using the tool.

An FPGA is made up of a combination of Logic Blocks, IO Blocks and interconnections wiring everything up.

Each logic block is made up of a variety of different primitive components interconnected, usually this consists of a Look Up Table, Multiplexer and some combinational logic. Below is a very simple CLB from an early Xilinx FPGA.

Now the important thing for me are the primitive components, which I have to model individually. Which in the case of the Xilinx XC2000, a very early FPGA is over 400 different components! Below is the same CLB but with the primitives highlighted.

Using an Event-Driven Discrete Modelling Simulation, these primitives were modelled and their interconnections simulated. Thus creating a working model.

No comments:

Post a Comment